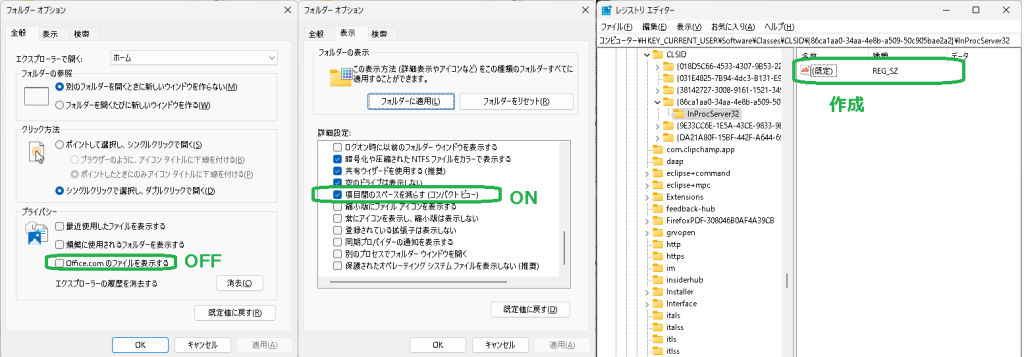

VB6アプリを再ビルドしたいと相談があり調べました。ExeclをVB6から操作するとき、COMコンポーネント( Windows上で世界でユニークなオブジェクトを示すID:CLSIDとそのインターフェイスをレジストリに登録することで呼出すソフトウェアコンポーネント) として Execl.exe を登録して呼出すようです。※イマドキではもっと簡単に Python でも可能なようです。

Dim execlApp As Excel.Application

Dim execlBook As Excel.Workbook

Dim execlSheet As Excel.Worksheet

Set execlApp = CreateObject("Excel.Application")

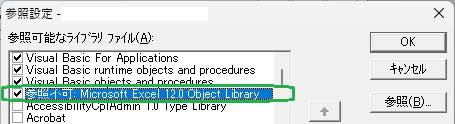

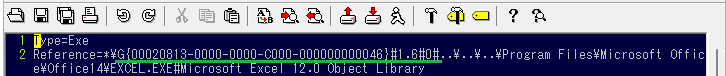

Execl2024での調査

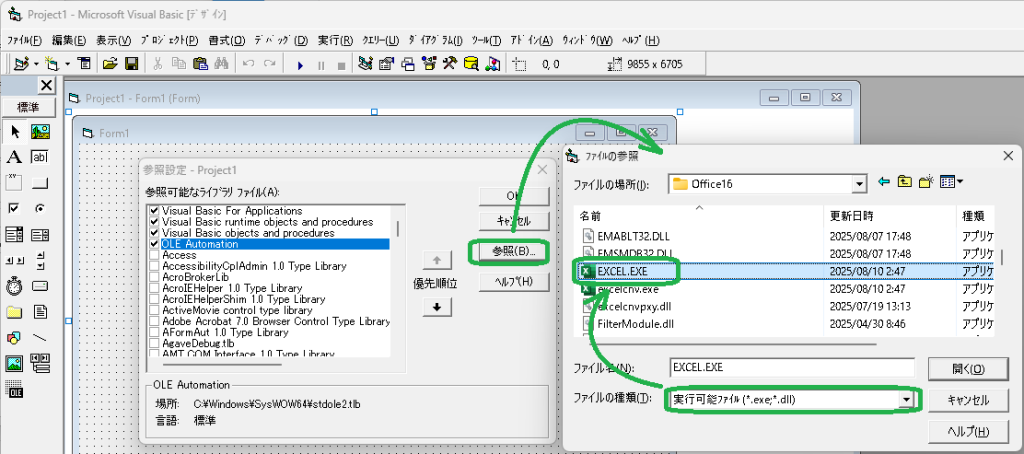

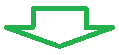

これをBuildする場合、Execlの本体が必要なようです。Execlはバージョン毎に収録先が異なります。Execl2024の場合、設定は以下のようになります。

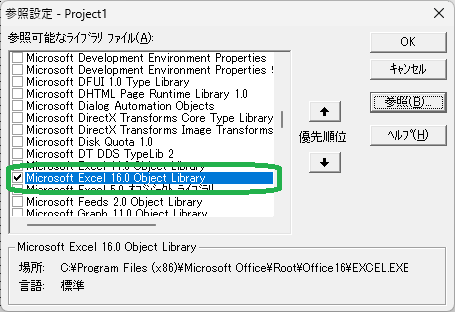

紐づけられるCOMコンポーネントはバージョンが明示されています。.VBP をみると、

CLSIDは 00020430-0000-0000-C000-000000000046 のようです。内部バージョンは 2.0。

アプリが複数のWindows PCで実行されると、そのPC毎に Execl の格納先とバージョンは異なるハズです。通常この設定を行うと、アプリ実行時、このパス固定参照されるか、レジストリ上に登録されている同じコンポーネントが呼び出されます。EXECLバージョン毎にCLSIDは同じなのでしょうか? .VBP で管理されるライブラリバージョンが一致しなくても動作するのでしょうか?

Execl2007では?

オリジナルの参照設定と .VBP をみると、Execl 2007 (内部version12)でした。CLSIDは同じですが、内部バージョンは1.6 でした。

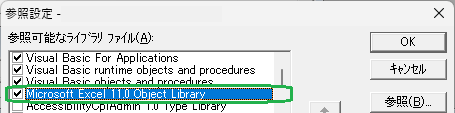

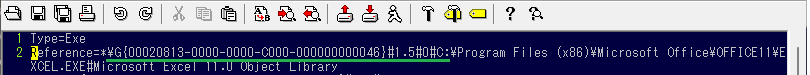

Execl2003では?

試しに Execl 2003(内部version11) を設定してみた結果です。CLSIDは同じ、内部バージョンは1.5 で

動作結果

以下動作結果です。

| PC | Build時のExecl設定 | 呼出されたExecl |

| Win11 Execl2003 & 2024同居 | 2003 | 2024 |

| Win11 Execl2003 & 2024同居 | 2007 | 2024 |

| Win11 Execl2003 & 2024同居 | 2024 | 2024 |

| Win11 Execl2003のみ | 2003 | 2003 |

| Win11 Execl2003のみ | 2007 | 2003 |

| Win11 Execl2003のみ | 2024 | 2003 |

動作原理をまとめると、

- CLSIDの一致はみるが、バージョンは照合しない。

- 上位互換性はあり。

- 複数Execlがインストールされている場合は、新しいExeclの方が呼び出される。

- VB6 IDE用のExeclバージョンは問われない。

ただし、新しいExeclで追加されたオブジェクト、methodは使えないのでしょうから、開発時のExeclに近いバージョンを使った方が無難と思います。( methodインターフェイスがかわるとmethodのCLSIDが変わるが、VBAオブジェクトヘルプにもmethod毎に対応バージョンまでは明記されておらず、それらを全部調べるのは現実的ではないため )

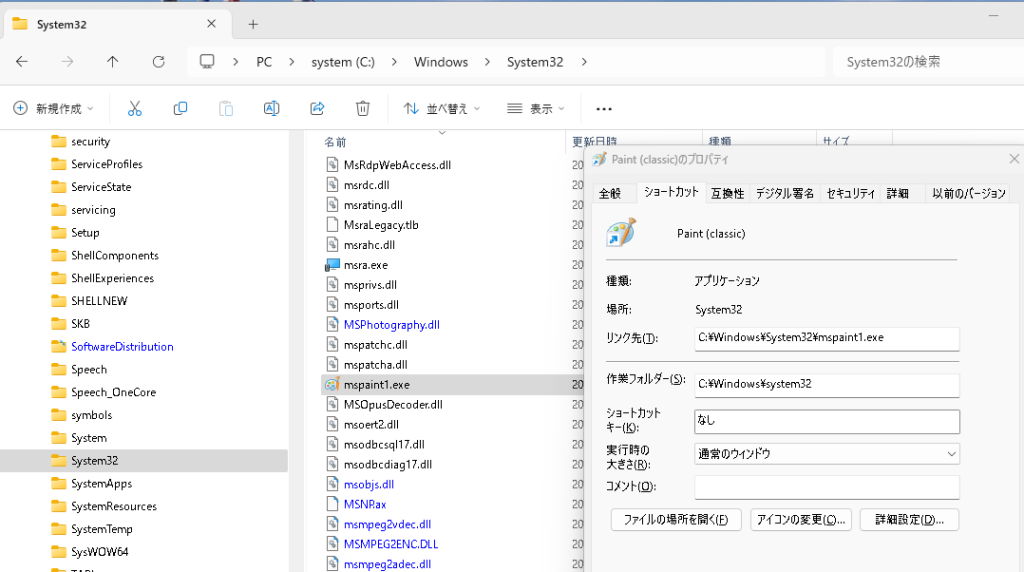

しかしながら、.NETアプリでありながら、COMコンポーネントあわせもつEXEを作れるんですね。